CHERIoT,un proyecto de Microsoft para mejorar la seguridad en C

CHERIoT, una opcion de MS para la seguridad para sistemas integrados

Hace poco se dio a conocer la noticia de que, Microsoft ha abierto los desarrollos relacionados con el proyecto CHERIoT (Capability Hardware Extension to RISC-V for Internet of Things), destinado a bloquear problemas de seguridad en código C y C++ existente. CHERIoT ofrece una solución para proteger las bases de código C/C++ existentes sin tener que refactorizarlas.

La protección se implementa mediante el uso de un compilador modificado que usa un conjunto extendido especial de instrucciones de procesador (ISA) proporcionado por el procesador y monitorea el acceso a la memoria a nivel de hardware, verifica la corrección del trabajo con punteros y proporciona aislamiento de bloques de código.

Sobre CHERIoT

El proyecto se creó con el entendimiento de que la naturaleza de bajo nivel del lenguaje C se convierte en una fuente de errores de memoria, lo que genera problemas como desbordamientos de búfer, acceso a memoria ya liberada, desreferenciación de punteros o liberación doble.

La práctica muestra que incluso las grandes corporaciones como Google y Microsoft, que tienen una política estricta de revisión de cambios y utilizan métodos de desarrollo modernos y herramientas de análisis estático, no pueden garantizar la ausencia de errores al trabajar con la memoria (por ejemplo, alrededor del 70 % de las vulnerabilidades en Microsoft y Google son causados por el manejo inseguro de la memoria).

El problema se puede resolver mediante el uso de lenguajes de programación que garanticen un trabajo seguro con la memoria o enlaces con controles adicionales, por ejemplo, mediante el uso de MiraclePtr (raw_ptr) en lugar de punteros comunes, que realiza controles adicionales para acceder a las áreas de memoria liberadas.

Pero tales métodos son más adecuados para código nuevo y es bastante problemático volver a trabajar en proyectos C/C++ existentes, especialmente si están destinados a ejecutarse en entornos con recursos limitados, como sistemas integrados y dispositivos IoT.

Los componentes de hardware de CHERIoT están diseñados como un microcontrolador basado en la arquitectura RISC-V, implementando la arquitectura de procesador segura CHERI (Extensión de hardware de capacidad para RISC-V), proporcionando un modelo de acceso a memoria controlado.

Basado en la arquitectura del conjunto de instrucciones (ISA) proporcionada en CHERIoT, se construye un modelo de programación que garantiza la seguridad de trabajar con la memoria a nivel de objetos individuales, brinda protección contra el acceso memoria ya liberada e implementa un sistema de aislamiento ligero acceso a la memoria.

Este modelo de protección mediante programación se refleja directamente en el modelo de lenguaje C/C++, lo que permite que se use para proteger aplicaciones existentes (solo se requiere la recompilación y la ejecución en hardware compatible con ISA CHERIoT) .

La solución propuesta permite bloquear errores que causan fuera de los límites de un objeto en la memoria, no permite la sustitución de punteros (todos los punteros deben generarse a partir de punteros existentes), monitorea el acceso a la memoria después de la liberación (cualquier acceso a la memoria por un puntero incorrecto o un puntero que hace referencia a un objeto liberado genera una excepción).

Por ejemplo, el uso de CHERIoT permite, sin realizar cambios en el código, implementar la verificación automática de límites, rastrear la vida útil de las áreas de memoria y garantizar la integridad de los punteros en los componentes que procesan datos no confiables.

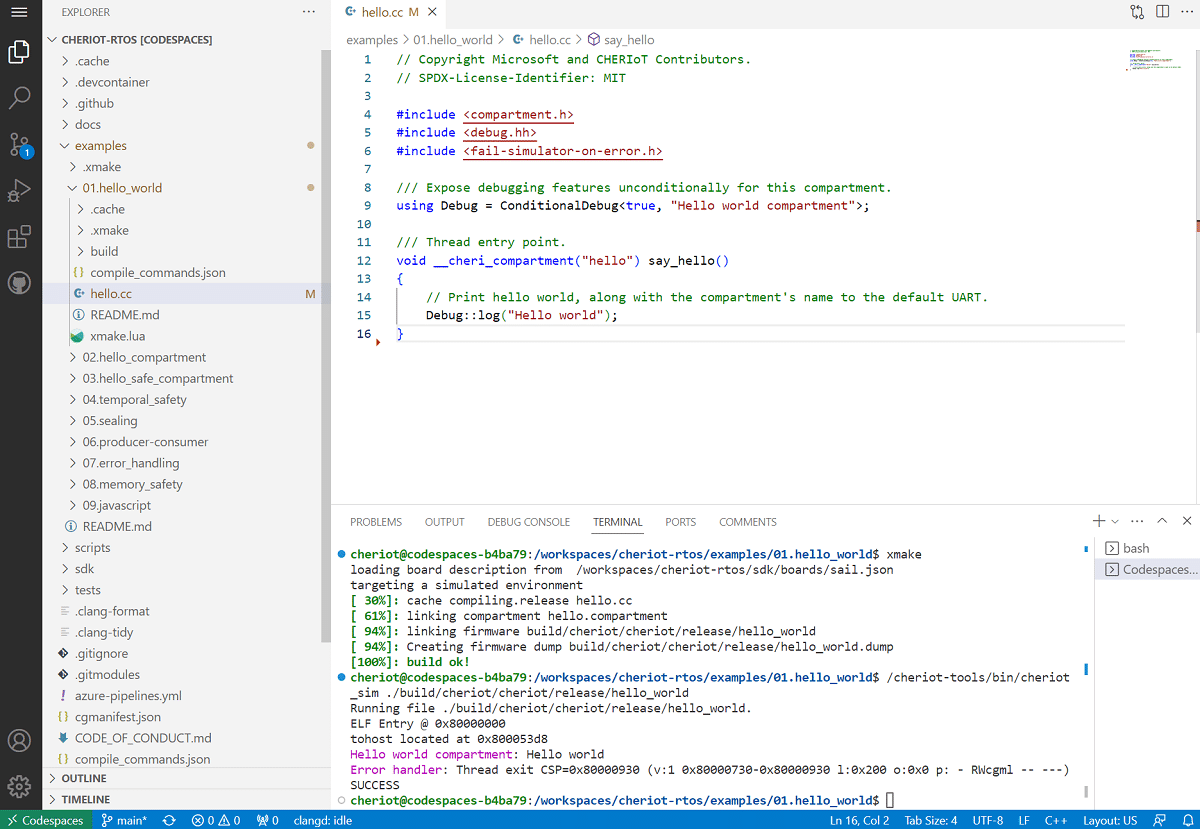

El proyecto incluye una especificación para una arquitectura de conjunto de instrucciones CHERIoT extendida, una implementación de referencia de una CPU RISC-V de 32 bits compatible con ISA CHERIoT y un conjunto de herramientas LLVM modificado.

Finalmente si estás interesado en poder conocer más al respecto, debes saber que los diagramas de prototipos de CPU y las descripciones de bloques de hardware en Verilog se distribuyen bajo la licencia Apache 2.0. El núcleo Ibex del proyecto lowRISC se utiliza como base para la CPU y el modelo de código CHERIoT ISA se define en el lenguaje Sail y se distribuye bajo la licencia BSD.

Adicionalmente, se propone un prototipo de sistema operativo en tiempo real CHERIoT RTOS , que brinda la capacidad de aislar compartimentos (compartment) incluso en sistemas embebidos con 256 MB de RAM.

El código CHERIoT RTOS está escrito en C++ y se distribuye bajo la licencia MIT. En forma de compartimentos, se diseñan los componentes básicos del sistema operativo, como el cargador de arranque, el programador y el sistema de asignación de memoria.