XiangShan, el procesador RISC-V chino que supera al Cortex-A75

Hace pocos dias el Instituto de Tecnología Informática de la Academia de Ciencias de China dio a conocer el proyecto XiangShan, en el cual se ha estado desarrollando desde el 2020 un procesador abierto de alto rendimiento basado en la arquitectura de conjunto de instrucciones RISC-V (RV64GC) y cuyo rendimiento se acerca a la velocidad del último núcleo Performance P550 de SiFive.

Hace pocos dias el Instituto de Tecnología Informática de la Academia de Ciencias de China dio a conocer el proyecto XiangShan, en el cual se ha estado desarrollando desde el 2020 un procesador abierto de alto rendimiento basado en la arquitectura de conjunto de instrucciones RISC-V (RV64GC) y cuyo rendimiento se acerca a la velocidad del último núcleo Performance P550 de SiFive.

Según los desarrolladores, los núcleos RISC-V que subyacen a la CPU Xiangshan se volverán tan populares entre los diseñadores de procesadores como lo es Linux para los sistemas operativos. Xiangshan será fabricado utilizando una tecnología de proceso de 28 nm por TSMC taiwanés (a menos que Estados Unidos imponga sanciones) y esta será la primera generación de núcleos con nombre en código Yanqi Lake.

RISC-V proporciona un sistema de instrucción de máquina abierto y flexible que le permite crear microprocesadores para aplicaciones arbitrarias sin requerir regalías o imponer condiciones de uso. RISC-V le permite crear SoC y procesadores completamente abiertos.

Actualmente, sobre la base de la especificación RISC-V, varias empresas y comunidades bajo diversas licencias libres (BSD, MIT, Apache 2.0) están desarrollando varias docenas de variantes de núcleos de microprocesadores, SoC y chips ya fabricados.

Sobre XiangShan

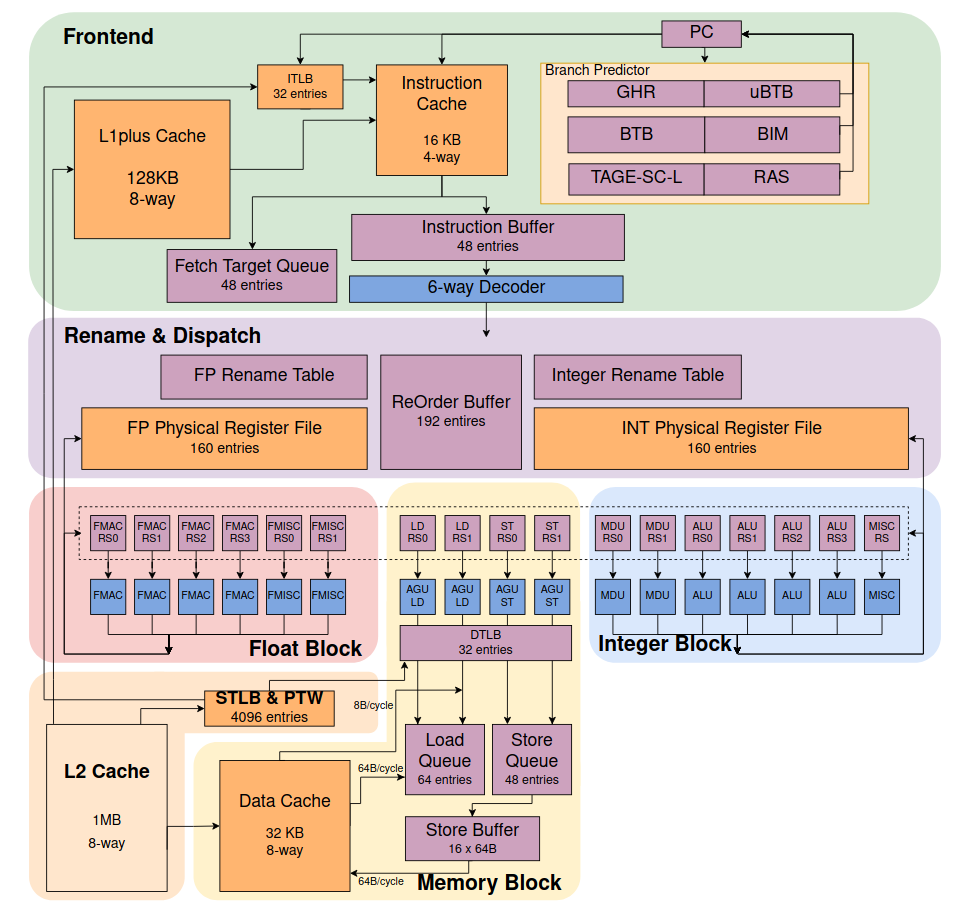

El proyecto se ha publicado bajo una descripción de bloques de hardware en el lenguaje Chisel, que se traduce a Verilog, una implementación de referencia basada en FPGA e imágenes para simular el funcionamiento de un chip en un simulador Verilog abierto.

«Aunque nuestro objetivo a largo plazo en el futuro es estar en línea con [Cortex-] A76, todavía está en progreso. Necesitamos una optimización iterativa con los pies en la tierra. El propósito del desarrollo ágil no es adelantar una esquina. La experiencia acumulada por Intel y Arm a lo largo de los años, también tenemos que acumularla lentamente «.

Los esquemas y las descripciones de la arquitectura también están disponibles (más de 400 documentos y 50 mil líneas de código en total), pero la mayor parte de la documentación está en chino, además de que Debian se utiliza como sistema operativo de referencia para probar la implementación de FPGA.

XiangShan afirma ser el chip RISC-V de mayor rendimiento, superando al SiFive P550. Las pruebas de FPGA están programadas para completarse este mes y el nombre en código «Yanqi Lake» es un chip prototipo de 8 núcleos que funciona a 1,3 GHz y se fabrica en TSMC utilizando la tecnología de proceso de 28 nm.

«Tenemos la esperanza de que XiangShan pueda sobrevivir durante 30 años», afirmó Bao, traducido, en una presentación reciente sobre el proyecto. «Tenemos un acuerdo para reunirnos nuevamente en 30 años y luego ver en qué se convertirá XiangShan. Sin embargo, para realizar este deseo, todavía hay muchos problemas y desafíos que deben resolverse».

El chip incluye una caché de 2 MB, un controlador de memoria con soporte para memoria DDR4 (hasta 32 GB de RAM) y una interfaz PCIe-3.0-x4.

El rendimiento del primer chip en el benchmark SPEC2006 se estima en 7/Ghz, que corresponde a los chips ARM Cortex-A72 y Cortex-A73.

«El proceso de diseño ágil y la plataforma que construimos anteriormente respaldan a un equipo de desarrollo de más de 20 personas, lo que está lejos de ser suficiente», señaló Bao. «Lo que debemos considerar ahora es cómo construir un conjunto de procesos abiertos estandarizados, abiertos y de código abierto que puedan respaldar el desarrollo de una comunidad de código abierto de 2000 personas».

Para finales de año, está prevista la producción de un segundo prototipo «South Lake» con una arquitectura mejorada, que será producido por SMIC con una tecnología de proceso de 14nm y un aumento de frecuencia a 2 GHz.

Se espera que el segundo prototipo alcance un rendimiento de 10/Ghz en el banco de pruebas SPEC2006, que está cerca de los procesadores ARM Cortex-A76 e Intel Core i9-10900K, y supera al SiFive P550, la CPU RISC-V más rápida a 8.65 / Ghz.

Finalmente si estás interesado en conocer más al respecto puedes consultar el código fuente de XiangShan, el cual se ha publicado bajo la MulanPSL2, en GitHub.

Fuente: https://www.zhihu.com